- 專欄

文章專區

2023-07-19從摩爾定律看半導體產業近半世紀以來的發展

643 期

Author 作者

胡璧合/臺大電機系副教授,專長為前瞻奈米電子元件及記憶體,三個孩子的母親。

Take Home Message

• 1947 年,蕭克利、巴丁、布拉頓發明了電晶體。它像一個微型開關,在訊號輸入時打開或關閉電晶體,就能決定是否讓訊號通過。

• 增加晶片單位面積上電晶體的數量可降低每個電晶體的成本,並提升晶片效能。「摩爾定律」預測了晶片上可放置的電晶體數量,約每隔18 ~ 24個月會增加一倍。

• 縮小電晶體尺寸可能造成短通道效應、穿隧效應等問題,提升晶片運算速度、降低功率消耗等訴求,也將會成為半導體持續研發的重要方向及挑戰。

仔細觀察一下周遭環境,你很難在觸手可及的範圍內找到不含電晶體(transistor)的裝置,幾乎所有電子產品都充滿了電晶體。電晶體在1947 年12 月,由美國貝爾實驗室(Nokia Bell Labs)的三位科學家⸺布拉頓(Walter Brattain)、蕭克利(William Shockley)、巴丁(John Bardeen)所發明,而他們也在1956 年獲得了諾貝爾物理獎。

什麼是電晶體?

去(2022)年12 月,全球半導體領域專家及電子元件協會(IEEE Electron Device Society)都在慶祝電晶體發明滿75 週年。75 年是一段很長的時間,以致於大多數人都早已忘記電晶體還未被發明之前的日子,而這段時間也足以讓許多科學家及工程師投入電晶體的使用及開發。電晶體可以被視為一個微型開關,當訊號輸入時,透過打開或關閉電晶體就能決定要不要讓訊號通過,藉此表現出數位訊號(0 或1)的特性。除了作為微型開關之外,電晶體的另一個重要特性就是放大輸入訊號。相較於早期讓電子在真空容器內流動產生電路的真空管vacuum tube),電晶體的體積較小、需要的操作電壓也較低,因此可解決使用真空管製作的計算機因體積大帶來的熱與高功率消耗等問題。

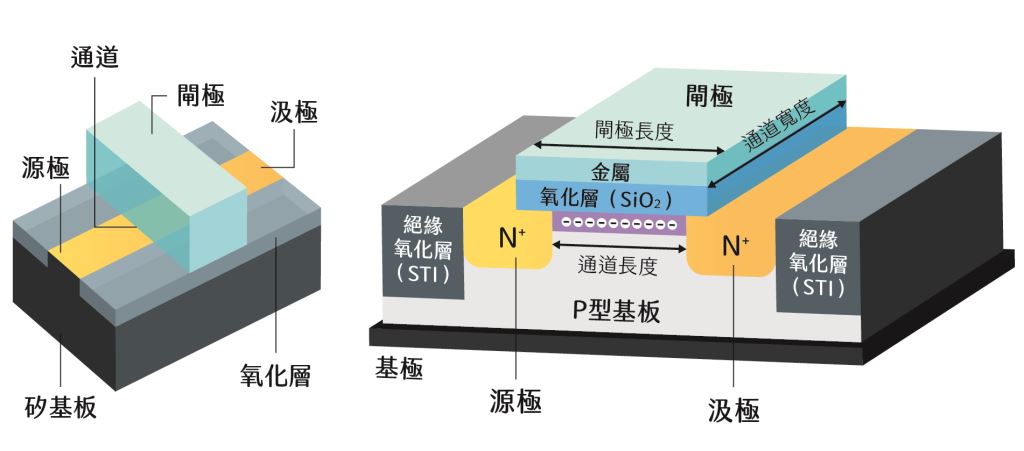

在電晶體中,最常見的種類為「金屬-氧化物-半導體場效電晶體」(metal-oxide-semiconductorfield-effect-transistor, MOSFET,簡稱金氧半場效電晶體),意指從電晶體最上層到下層的材料分別是金屬閘極、氧化層、半導體材料。MOSFET 的基本組成架構包含閘極(gate)金屬與氧化物堆疊層、通道區域、源極(source)、汲極(drain)。源極和汲極經過化學摻雜(doped)後,含有大量可移動且帶負電荷的電子,因此源極和汲極被稱為N 型半導體區域;通道區域則透過摻雜使它帶有正電荷,稱為P 型半導體區域。也因為能藉由電場效應打開或關閉電晶體,因此MOSFET 又被稱為「場效電晶體」(field-effect transistor,FET)。當對閘極施加足夠大的電壓後,即可在通道區域形成一層可移動的電子層,再透過施加於汲極的正電壓,進而使此電子層在源極和汲極之間流動(圖一)。此時,矽基板的表面將形成一個平面電流通道(也就是打開電晶體);當移除閘極的電壓後,通道區域便無法形成導通電子層,即為關閉電晶體。

電晶體的結構與電子的流動方式

對閘極施加足夠大的電壓後,即可在通道區域形成一層可移動的電子層,再透過施加於汲極的正電壓,使得此電子層在源極和汲極之間流動,此結構又被稱為平面式金氧半場效電晶體(planar MOSFET)。

更輕薄的積體電路

約在1958 ~ 1959 年,當時任職於美國科技公司德州儀器(Texas Instruments)的物理學家基爾科比(Jack Kilby)及半導體公司英特爾(Intel)創辦人之一的諾伊斯(Robert Noyce),同時提出積體電路(integrated circuit, IC)的概念。積體電路又稱為晶片(chip),要能成功製作出積體電路,需要達成三大要求:第一、將不同的電子元件,如電晶體、電阻、電容等整合(integration)在單一的半導體基板上;第二、在同一個半導體基板上的各個電子元件,彼此之間需要互相隔離(isolation);第三、在各個電子元件之間形成電性上的連接(connection)。

透過將電晶體和其他電子元件整合在單一個矽基板上,就可以提升整體電路的性能並縮小積體電路尺寸,諾伊斯提出在矽基板上成長絕緣氧化層,於氧化層上沉積金屬導線以連接不同的電子元件,此概念也較貼近現代的積體電路技術。在1960 年代,美國積極發展登月計畫時,阿波羅導航電腦(Apollo Guidance Computer, AGC)使用體積較小且重量較輕的積體電路技術,被認為是美國國家航空暨太空總署(National Aeronautics and Space Administration, NASA)登月計畫得以成功的原因之一。

什麼是摩爾定律?

1965 年, 同為英特爾創辦人之一的摩爾(Gordon Moore),發表一篇題目為〈在積體電路中塞入更多元件〉(Cramming more components ontointegrated circuits)的文章,摩爾在文章中提出晶片上可放置的電晶體數量,每隔一年會增加一倍;1975 年,他修正此預測為每兩年增加一倍。此外,摩爾在此文章中也提到,由於矽(silicon,Si)為地殻中含量豐富且相對便宜的元素,將成為製作積體電路時最主要的半導體材料。後來半導體界對此預測改為在相同晶片面積上,每18 ~ 24個月電晶體數量會增加一倍,透過增加單位面積上電晶體的數量,可降低每個電晶體的成本並提升晶片效能。加州理工學院(California Institute of Technology)的科學家米德(Carver Mead)將此預測稱為「摩爾定律」(Moore's Law)。

摩爾在1965 年的一篇文章中,首次提出晶片上可放置的電晶體數量,每隔一年會增加一倍。後來半導體業界將此預測改為在相同晶片面積上,每18 ~ 24 個月電晶體數量會增加一倍,並將此預測稱為「摩爾定律」。(OnInnovation, Henry Ford, CC BYND2.0, Flickr, https://bit.ly/42DhrtA)

英特爾也在1971年推出第一款商用微處理器Intel 4004,內含2300 個電晶體,採用10 微米(μm)製程技術。而在去(2022)年Apple 發表的Apple A16 仿生晶片(Apple A16 Bionic),則內含160億個電晶體,使用加強版5 奈米(nm)製程技術,可見從1971 ~ 2022 約50 年之間,晶片上可容納的電晶體數量有極顯著的增加。若想要在相同晶片面積上放置更多的電晶體,就代表電晶體尺寸需要不斷的微縮,而電晶體尺寸微縮靠的則是製程技術持續的突破、新材料的應用、電晶體結構的創新。傳統上,製程技術或技術節點(technology node)代表的是電晶體閘極長度(gate length),當製程技術節點的數字變小,就代表製程能力進步,可縮小閘極長度和電晶體尺寸,進而增加電晶體密度。然而,在縮短平面式MOSFET 的閘極長度時,源極和汲極之間的距離也將隨之變小,使得在關閉電晶體的情況下,仍會有源極和汲極間的漏電流產生,導致額外的功率消耗,降低電晶體和整體晶片的性能表現。

2011年,英特爾在22奈米技術節點提出使用三閘極(tri-gate)包覆通道的電晶體結構(圖二),此時技術節點的數字已經無法代表電晶體的閘極長度……【更多內容請閱讀科學月刊第643期】